Samsung、EUV SRAMでIntelを凌ぐ?:メモリベンダーとしての意地も

Samsung Electronicsは「ISSCC 2018」で、SRAMに適用するEUV(極端紫外線)技術に自信を見せた。一方のIntelは、EUVには相当慎重になっている。

EUVに自信を見せるSamsung

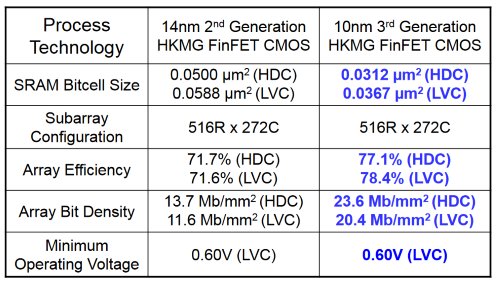

Intelは、2018年2月11~15日に米国カリフォルニア州サンフランシスコで開催された半導体集積回路技術の国際会議「ISSCC(IEEE International Solid-State Circuits Conference) 2018」で「ムーアの法則のスケーリングは、10nm SRAMで継続できる」と主張した。一方、Samsung Electronicsは、EUV(極端紫外線)リソグラフィを適用した、より小型の256MビットSRAMについて説明し、EUV技術に対する自信を示した。

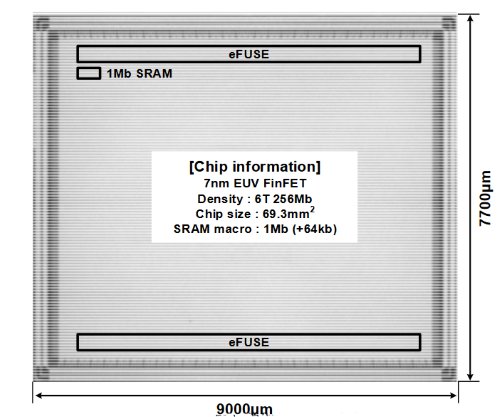

Intelは、10nmプロセスを適用したビットセル面積が0.0312μm2の高密度SRAMと、0.0367μm2の低電圧SRAMについて説明した。Samsungの256Mビットチップは、記憶容量が6Tバイトで、ビットセル面積は0.026μm2だという。

Intelの設計は、14nm SRAMと比べて0.62~0.58倍の微細化を達成し、ムーアの法則を維持している。IntelのZheng Gui氏は、Samusungが2018年に発表した7nm SRAMとTSMCが「ISSCC 2017」で発表した7nm SRAMと比較して、「最小と報告されている7nmセルとの差は15%以下だ」と述べている。

一方のSamsungは、EUVでSRAMを量産できるのだろうか。Samsungの設計担当バイスプレジデントで同設計論文を発表したTaejoong Song氏は、「実際に動作するチップを実現できたことで、懸念が軽減した」と述べている。

同論文は、設計上で最大の課題の1つであるビット線抵抗を75%軽減する手法について説明している。Song氏は、「EUVは、使用するビアの数に関して、より柔軟な設計が可能だ」と述べている。

Song氏はプレゼンテーション終了後、よく知られている評価基準のPPA(Power, Performance, Area:消費電力、性能、チップ面積)を使って、「EUVによってチップ面積を縮小し、設計技術で消費電力と性能を高めた」と説明した。

また、十分に検証された設計の下、少なくとも4~6層にEUVを適用したことも明らかにした。ただし、Song氏は、EUVの商用利用に関する同社の計画については特に新しい情報は明かさなかった。

ISSCC 2018に参加したあるアナリストは、「私が最も気に掛かっているのは、Intelが後れを取っていることだ」と懸念を示した。他のアナリストは、SamsungのEUV SRAM技術について懐疑的な見方を示している。米国の調査会社である Real World TechのDavid Kanter氏は、「TSMCとIntelは、EUVに関してSamsungよりかなり慎重で、それには相応の理由があると思われる。これまでにEUVウエハーを手掛けた企業の少なさを考えれば、歩留まりに問題があると考えざるを得ない」と述べている。

ISSCC 2018に参加したNAND型フラッシュメモリのパイオニアであるEli Harari氏は、「Samsungはメモリベンダーとして、SRAMのサイズをIntelよりも気に掛けている」と述べている。同氏は、「次世代以降の半導体におけるEUVの潜在的なリターンは非常に大きいが故に、大手半導体メーカーは、そのリターンと、EUVのコストおよび技術的な課題のはざまで苦しむことになるかもしれない」と述べている。

【翻訳:滝本麻貴、編集:EE Times Japan】

Copyright © ITmedia, Inc. All Rights Reserved.

記事ランキング

- Intel低迷でSamsungが笑う? パッケージングのエース級人材が移籍

- 「AppleがSamsungから半導体調達」報道、ソニーの反応は

- 2024年のイメージセンサー市場もソニーがトップ、高まる中国の存在感

- HDD大手WDの四半期業績、前期比で増収ながらも増減益は微妙

- 「GaNのコストは5年以内にSi並みに」 ロームの勝ち筋は

- タイワン・セミコンダクターがSiCパワー半導体市場に参入、その狙いは

- 対中輸出規制のほころび、CadenceがEDAツールを違法販売

- 世界半導体製造装置市場、2026年は過去最高に

- 追加学習や構造変更なしでLLMの推論速度を4倍に

- スパッタ法で高品質ScAlN薄膜の作製に成功

14nm HKMG(High-k/メタルゲート) FinFET CMOSプロセスと、同10nmプロセスをSRAMの製造に適用する際の比較 出典:Intel

14nm HKMG(High-k/メタルゲート) FinFET CMOSプロセスと、同10nmプロセスをSRAMの製造に適用する際の比較 出典:Intel Samsungが完全に動作を確認したという、EUVを適用して試作した256MビットSRAM 出典:Samsung

Samsungが完全に動作を確認したという、EUVを適用して試作した256MビットSRAM 出典:Samsung 東北大学ら、次世代相変化メモリの新材料を開発

東北大学ら、次世代相変化メモリの新材料を開発 1MビットFeRAM、モバイルやIoT機器への応用も

1MビットFeRAM、モバイルやIoT機器への応用も 「不揮発性DRAM」へのアプローチ(前編)

「不揮発性DRAM」へのアプローチ(前編) EUVが実現間近か、250Wの光源を達成

EUVが実現間近か、250Wの光源を達成 EUVの量産適用、半導体業界は前向きな見方

EUVの量産適用、半導体業界は前向きな見方 ASML、EUVリソグラフィ開発を加速

ASML、EUVリソグラフィ開発を加速