CMOSイメージセンサーが引っ張る3次元積層技術:ビジネスニュース 業界動向(1/2 ページ)

チップを積層し、TSV(シリコン貫通電極)などで接続する3次元IC技術。CMOSイメージセンサーでも、3次元化が進んでいる。

これまで最先端プロセス技術の分野でリーダー的な位置付けを獲得してきたのは、プロセッサやメモリだ。しかし現在、CMOSイメージセンサーがそれに取って代わろうとしている。スマートフォンやタブレット端末、医療用機器、自動車など、あらゆる市場において、CMOSイメージセンサーの需要が高まっているためだ。

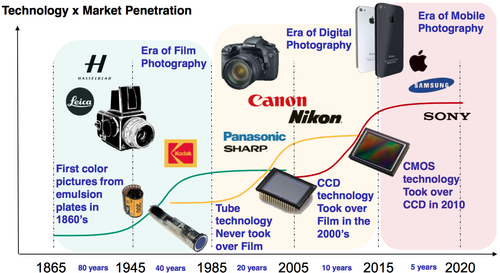

イメージング技術ではかつて、フィルムが使われていた。しかし、固体撮像素子が出現したことによって飛躍的な成長を遂げてきた。

注目集まる3次元IC

こうした中で成長しているのが、3次元(3D)積層技術だ。例えば、Micron Technologyの「Hybrid Memory Cube(HMC)」は、コントローラとDRAMチップをシリコン貫通電極(TSV:Through Silicon Via)で接続している。だが、CMOSイメージセンサーでは、ピクセルアレイ用に金属相互接続配線されたウエハーの、銅-銅接合(copper-to-copper bonding)を実現した点で、プロセッサやメモリにおける3次元積層技術の一歩先を行っているといえるだろう。

フランスの市場調査会社Yole DéveloppementのアナリストであるPierre Cambou氏は、EE Timesのインタビューに対し、「現在のところ、3次元積層では、上のウエハーと下のウエハーを接続するのに、TSV技術を採用している。2つのビアは、それぞれの接続に不可欠であり、2層間を橋渡しする役割を担う。2つのビア間の金属結合は、チップの表面で行っている」と述べている。

銅-銅接合でレイヤー間を接続できるようなウエハー積層技術が完成すれば、CMOSイメージング業界は、プロセッサ/メモリ業界ではまだ普及すらしていないTSV技術が“時代遅れ”になってしまう可能性もあるのだ。

Copyright © ITmedia, Inc. All Rights Reserved.

Special Contents

- PR -Special Contents

- PR -Special Contents 1

- PR -Special Contents 2

- PR -記事ランキング

- TSMCがGaN事業撤退へ、ロームは「さまざまな可能性を協議」

- 講演会場が静まり返った――中国が生み出した衝撃のトランジスタ構造

- TSMCがGaNファウンドリー事業から撤退へ、NavitasはPSMCと提携で対応

- 26年度には世界大手の9割が採用、黒字化も 本格化するソニーの車載イメージセンサー

- 25年5月の世界半導体市場は全地域で成長、19.8%増の590億ドルに

- 危うい再建計画 Wolfspeed、CHIPS法補助金で再生図るか

- 半導体製造ラインの立ち上げ迅速に、日本IBMが京都に開発拠点

- Qualcommの狙いは何なのか、やたらと「高い」Alphawave買収額

- 「DRAM生産の4割を米国で」 Micronを待ち受ける過酷な競争

- 22nmプロセス採用でMRAM内蔵、ルネサスがエッジAI特化の新マイコン

イメージング技術の推移 出典:Yole Développement

イメージング技術の推移 出典:Yole Développement