シリコンインターポーザを導入した高性能パッケージの製品例:福田昭のデバイス通信(108) TSMCが解説する最先端パッケージング技術(7)(1/2 ページ)

シリコンインターポーザを導入したパッケージの製品化時期は、おおむね、2012年の第1期と、2015~2016年の第2期に分けられる。それぞれの時期を代表する製品例と、それらの特徴を紹介する。

2012年から始まったシリコンインターポーザ技術の製品化

2016年12月に開催された国際学会IEDMのショートコース講演(技術解説講演)から、「システム集積化に向けた最先端パッケージング技術(Advanced Packaging Technologies for System Integration)」と題する講演の概要をシリーズでご紹介している。講演者はシリコンファウンドリー最大手のTSMCでシニアディレクターを務めるDouglas Yu氏である。なお講演内容だけでは説明が不十分なところがあるので、本シリーズでは読者の理解を助けるために、Yu氏の講演内容を筆者が適宜、補足している。あらかじめご了承されたい。

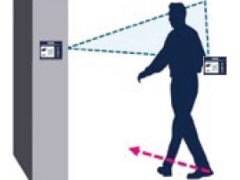

前回は、TSMCが開発した高性能・高密度パッケージング技術「CoWoS(Chip on Wafer on Substrate)」の構造と製造工程を説明した。今回は、CoWoS技術を含めた、シリコンインターポーザ技術のパッケージを製品化した事例をご報告する。

製品化の時期はおおむね、2つに分かれている。2012年の第1期と、2015年~2016年の第2期である。

ロジックダイの分割搭載と、ロジックとメモリ混載にCoWoSを適用

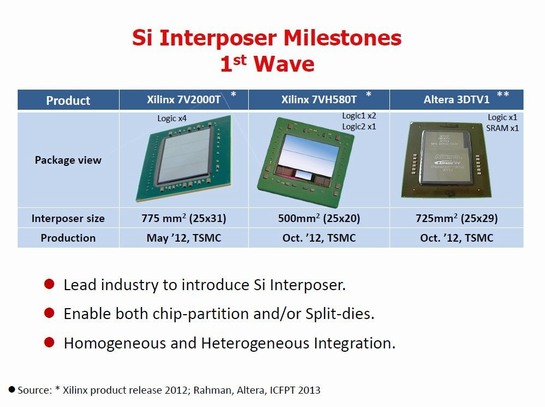

2012年の第1期では、FPGAの大手ベンダーであるXilinxとAltera*)がそれぞれ、ハイエンドの製品シリーズ向けにTSMCのCoWoS技術を採用した。

*)旧Alteraの製品は、Intelが2015年12月にAlteraを買収したことにより、現在は「Intel FPGA」ブランドとして販売されている。

Xilinxは28nm世代のFPGA「Virtex-7」シリーズの「2000T」に、4枚の同一サイズのFPGAロジックダイをシリコンインターポーザに近接して搭載したパッケージを導入した(関連記事:「ザイリンクス、28nm世代の次期FPGAで3次元パッケージを採用」)。同社は「Virtex-7」シリーズの「7 VH580T」にも、大きなロジックダイ(FPGA)を2枚と小さなロジックダイ(トランシーバー)を1枚、シリコンインターポーザに近接して搭載したパッケージを導入している。Alteraは、FPGAシリコンダイとSRAMシリコンダイをシリコンインターポーザに搭載した(関連記事:「“シリコンコンバージェンス”へ、3次元FPGAの取り組みをAlteraが説明」)。

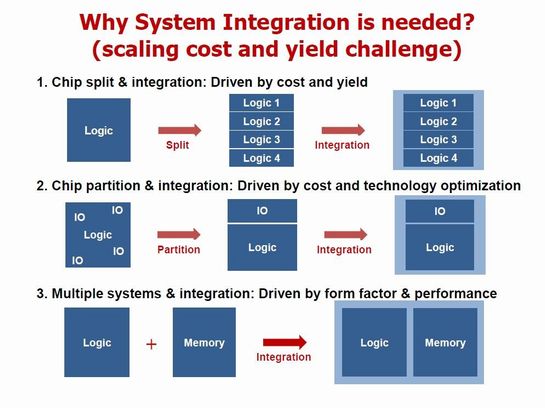

XilinxとAlteraの違いは、Xilinxがワンチップには収容困難なほど大規模なFPGAロジックを複数のシリコンダイに分割していることに対し、Alteraはロジックとメモリという異なる種類のシリコンダイを集積していることにある。下記にも示したが、本シリーズの第2回で説明した図面の1番がXilinxの事例、3番がAlteraの事例に対応していることが分かる。

Copyright © ITmedia, Inc. All Rights Reserved.

Special Contents

- PR -- [EE Times Japan驍ア�ィ鬮ョ�スホ咯 EE Times Japan��窮DN Japan 驍ィ�ア陷キ逎ッ蟠戊氛蜊�イソ�ス螢シ蛻磯ィセ貅倪�郢ァ荵敖蠕後℃郢晢スゥ郢ァ�ケ陜難スコ隴夲スソ邵イ蝓シ蟷暮具スコ邵イツ隴鯉ス・隴幢スャ郢ァ繧�ソ�郢ァ轣假スシ蜍滂スス�ケ邵コ�ォ遯カ陬慊�ス 鬮ョ�サ陝�鴻豐ソ2025陝キ�エ4隴帑コ・謐キ

- 鬮「迢怜験郢ァ蝣、�ー�。驍擾ソス陋ケ謔カ��驕カ�カ闔�迚咎エィ郢ァ雋橸スシ�キ陋ケ謔カ笘�ケァ荵敖竏ォ�ャ�ャ4闕ウ邏具スサ�」雎主ョ育舞USB郢晢ソス繝ー郢ァ�、郢ァ�ケ郢ァ�ウ郢晢スウ郢晏現ホ溽ケ晢スシ郢晢スゥ郢晢スシ邵コ�ョ陞ウ貅キ魘ィ

- 陷企宦�ー諠ケ�ス隰趣スク蟠取�髫暦ス」隴ォ闊鯉ソス隴�スー陟�ソス諷咲クイ竏夲ソス郢晢スュ郢ァ�サ郢ァ�ケ鬮「迢怜験郢ァ雋槫�鬨セ貅倪�郢ァ蛹コ�ャ�。闕ウ邏具スサ�」邵コ�ョ3D X驍ア螟撰ス。蜍滂スセ�ョ鬮�。邵コ�ョ陞ウ貅キ魘ィ

- 邵イ謔溷ア楢ャ壼・縺慕ケ晢スウ郢晏現ホ帷ケァ�ケ郢晏現繝ィ郢晢ス「郢ァ�ー郢晢スゥ郢晁シ斐≦邵イ髦ェ�帝$逧ョ�ゥ�カ陞ウ�、郢晢スャ郢晏生ホ晉クコ�ァ陞ウ貅ス讓溽クコ蜷カ�玖ュ�スケ雎戊シ披�邵コ�ッ�ス�ス

- [EE Times Japan驍ア�ィ鬮ョ�スホ咯 陷企宦�ー諠ケ�ス轣倩�驕会スセ 隶鯉スュ驍オ�セ邵コ�セ邵コ�ィ郢ァ竏堋�ス2025陝キ�エ3隴帛沺謔�圷�ャ3陜怜ク帶ソ�隴帶コ伉�ス

Special Contents 2

- PR -記事ランキング

- 半導体メーカーの「悲喜こもごも」 絶好調のTSMC、人員削減のST

- IntelがAltera売却へ、株式51%を米投資ファンドに

- 2024年の半導体市場は21%成長 NVIDIAが初の首位に

- ミネベアミツミが芝浦電子買収へ 「8本槍」戦略強化に向け

- 2035年のウエハー需要を予測する ~半導体も「VUCA時代」に

- 世界半導体市場が10カ月連続で17%以上成長 2月として過去最高に

- AIのデータ転送問題解決に王手、シリコンフォトニクス新興企業

- 1インチサイズの全固体電池を10秒で作製 レーザーで加工

- チップに「水路」を作り冷却液を流し込む 高効率に放熱

- トランプ政権の「アメとムチ」 Intelは補助金を受け取れるのか