「3D XPointメモリ」開発のオープン・モードとステルス・モード:福田昭のストレージ通信(148) 半導体メモリの技術動向を総ざらい(9)(1/2 ページ)

今回は、「3D XPointメモリ」の研究開発が、オープン・モードで始まり、後半はステルス・モードとなっていたことを説明する。

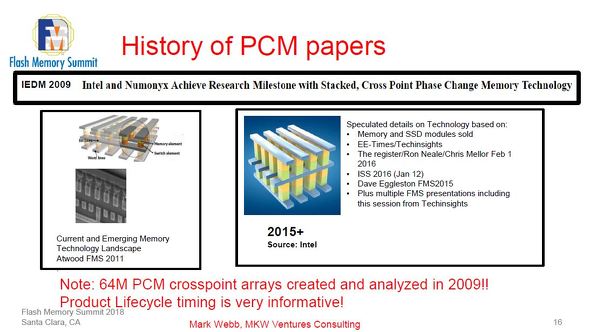

「3D XPointメモリ」の基本技術は2001年と2009年に学会で発表

2018年8月に米国シリコンバレーで開催された、フラッシュメモリとその応用製品に関する世界最大のイベント「フラッシュメモリサミット(FMS:Flash Memory Summit)」でMKW Venture Consulting, LLCでアナリストをつとめるMark Webb氏が、「Annual Update on Emerging Memories」のタイトルで講演した半導体メモリ技術に関する分析を、シリーズでご紹介している。

なお講演の内容だけでは説明が不十分なところがあるので、本シリーズでは読者の理解を助けるために、講演の内容を適宜、補足している。あらかじめご了承されたい。

前回は、相変化メモリ(PCM)が2013年に市場から一度消えた後に、2015年に「3D XPointメモリ」で劇的に復活したことをご報告した。今回は、「3D XPointメモリ」の研究開発が始めはオープン・モードであり、後半に入ってステルス・モードとなっていたことをご説明する。

本シリーズの第5回と第6回でご報告したように、次世代半導体製品の研究開発では、前半が研究成果の一部を公表するオープン・モード、後半がひそかに研究開発を進めるステルス・モードであることが少なくない。「3D XPointメモリ」の研究開発でも、オープン・モードの時代があったとみられる。

IntelとMicron Technology(以降はMicronと表記)が「3D XPointメモリ」の共同開発を発表したのは、2015年7月である。その5年半ほど前の2009年12月に、国際学会IEDMでIntelとNumonyx(IntelとSTMicroelectronicsの合弁企業、後にMicronによって買収された)がクロスポイント構造の相変化メモリ(PCM)を試作発表していたのだ。発表の概要は本コラムの姉妹コラム「福田昭のデバイス通信」で2016年1月にご紹介している(関連記事:「IEDMで発表されていた3D XPointの基本技術(前編)」)。

このとき発表されたクロスポイント構造のPCMは1層で、記憶容量は64Mビットだった。90nm世代の製造技術によって第2層金属配線と第3層金属配線の間に、クロスポイント構造のメモリセルアレイを作り込んだ。そしてセレクタ技術は、OTS(Ovonic Threshold Switch)だった。PCMとOTSの組み合わせという要素技術は、「3D XPointメモリ」と同じである。PCMとOTSの材料は公表していない。

メモリセルのスイッチング(書き込み)時間はリセット動作(高抵抗状態への相変化)のときに最短で9ナノ秒とかなり短い。そして読み書きのサイクル寿命(セット(低抵抗)状態でのしきい電圧で評価)は100万回に達していた。

さらにさかのぼると、2001年12月に国際学会IEDMでIntelとOvonyx社(相変化メモリの開発ベンチャー)が、PCM技術を共同発表していた。PCMのカルコゲナイド合金はGeSbTeである。この3元素の組み合わせは、「3D XPointメモリ」のPCMと変わらない。ただしIEDMでは組成比を公表していないので、組成比が同じであるかどうかは、不明である。

2009年12月の国際学会IEDMでクロスポイント構造のメモリが発表された後は、国際学会や学会論文誌などで「3D XPointメモリ」に関連する技術が発表された痕跡は見当たらない。すなわち、ステルス・モードに入ったとみられる。

Copyright © ITmedia, Inc. All Rights Reserved.

Special Contents

- PR -- [EE Times Japan驍ア�ィ鬮ョ�スホ咯 EE Times Japan��窮DN Japan 驍ィ�ア陷キ逎ッ蟠戊氛蜊�イソ�ス螢シ蛻磯ィセ貅倪�郢ァ荵敖蠕後℃郢晢スゥ郢ァ�ケ陜難スコ隴夲スソ邵イ蝓シ蟷暮具スコ邵イツ隴鯉ス・隴幢スャ郢ァ繧�ソ�郢ァ轣假スシ蜍滂スス�ケ邵コ�ォ遯カ陬慊�ス 鬮ョ�サ陝�鴻豐ソ2025陝キ�エ4隴帑コ・謐キ

- 鬮「迢怜験郢ァ蝣、�ー�。驍擾ソス陋ケ謔カ��驕カ�カ闔�迚咎エィ郢ァ雋橸スシ�キ陋ケ謔カ笘�ケァ荵敖竏ォ�ャ�ャ4闕ウ邏具スサ�」雎主ョ育舞USB郢晢ソス繝ー郢ァ�、郢ァ�ケ郢ァ�ウ郢晢スウ郢晏現ホ溽ケ晢スシ郢晢スゥ郢晢スシ邵コ�ョ陞ウ貅キ魘ィ

- 陷企宦�ー諠ケ�ス隰趣スク蟠取�髫暦ス」隴ォ闊鯉ソス隴�スー陟�ソス諷咲クイ竏夲ソス郢晢スュ郢ァ�サ郢ァ�ケ鬮「迢怜験郢ァ雋槫�鬨セ貅倪�郢ァ蛹コ�ャ�。闕ウ邏具スサ�」邵コ�ョ3D X驍ア螟撰ス。蜍滂スセ�ョ鬮�。邵コ�ョ陞ウ貅キ魘ィ

- 邵イ謔溷ア楢ャ壼・縺慕ケ晢スウ郢晏現ホ帷ケァ�ケ郢晏現繝ィ郢晢ス「郢ァ�ー郢晢スゥ郢晁シ斐≦邵イ髦ェ�帝$逧ョ�ゥ�カ陞ウ�、郢晢スャ郢晏生ホ晉クコ�ァ陞ウ貅ス讓溽クコ蜷カ�玖ュ�スケ雎戊シ披�邵コ�ッ�ス�ス

- [EE Times Japan驍ア�ィ鬮ョ�スホ咯 陷企宦�ー諠ケ�ス轣倩�驕会スセ 隶鯉スュ驍オ�セ邵コ�セ邵コ�ィ郢ァ竏堋�ス2025陝キ�エ3隴帛沺謔�圷�ャ3陜怜ク帶ソ�隴帶コ伉�ス

Special Contents 2

- PR -記事ランキング

- 半導体メーカーの「悲喜こもごも」 絶好調のTSMC、人員削減のST

- IntelがAltera売却へ、株式51%を米投資ファンドに

- 2024年の半導体市場は21%成長 NVIDIAが初の首位に

- 世界半導体市場が10カ月連続で17%以上成長 2月として過去最高に

- ミネベアミツミが芝浦電子買収へ 「8本槍」戦略強化に向け

- チップに「水路」を作り冷却液を流し込む 高効率に放熱

- 2035年のウエハー需要を予測する ~半導体も「VUCA時代」に

- AIのデータ転送問題解決に王手、シリコンフォトニクス新興企業

- トランプ政権の「アメとムチ」 Intelは補助金を受け取れるのか

- 1インチサイズの全固体電池を10秒で作製 レーザーで加工