EE Times Japan >

メモリ/ストレージ >

「3D XPointメモリ」開発のオープン・モードとステ...

「3D XPointメモリ」開発のオープン・モードとステルス・モード:福田昭のストレージ通信(148) 半導体メモリの技術動向を総ざらい(9)(2/2 ページ)

» 2019年06月05日 11時30分 公開

[福田昭,EE Times Japan]

「3D XPointメモリ」の性能を推定する

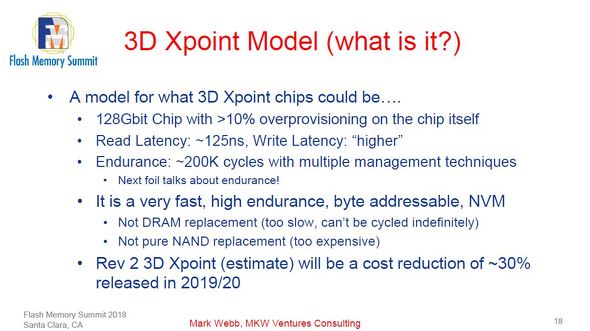

2009年12月に国際学会IEDMで試作発表されたクロスポイントメモリの内容と、2015年7月以降に「3D XPointメモリ」について明らかになった内容から、Webb氏は「3D XPointメモリ」の性能を以下のように推定してみせた。

公称の記憶容量は128Gビットである。ただし冗長ビット(予備のメモリセルアレイ)を備えている可能性が非常に高い。冗長ビットの割合は10%以上だと、Webb氏は見積もった。読み出し動作の遅延時間(レイテンシ)は約125ナノ秒であり、書き込み動作の遅延時間は読み出しよりも長い。書き換えサイクル寿命は約20万サイクルで、書き換えサイクルを延ばすための要素技術がいくつか、組み込まれているとする。書き換えの単位はバイト単位である。

高速で動作し、書き換え寿命の長いメモリではあるものの、DRAMとNANDフラッシュメモリのいずれも、「3D XPointメモリ」によって置き換えることは難しい。DRAMに比べると低速であることと、読み書き回数に制限があることが、DRAMの置き換えを妨げる。そしてNANDフラッシュメモリに比べると記憶容量当たりの製造コストが高いことが、NANDフラッシュメモリの置き換えを困難にする。

またIntelとMicronは「第2世代」の3D XPointメモリを開発中であり、2019年~2020年には発表されるもようだ。第2世代では、記憶容量当たりのコストを30%前後、低くするとされる。

(次回に続く)

⇒「福田昭のストレージ通信」連載バックナンバー一覧

関連記事

Copyright © ITmedia, Inc. All Rights Reserved.

Special Contents

- PR -Special Contents 1

- PR -記事ランキング

- DRAM業界をかき乱す中国勢、DDR4の供給の行方は?

- 半導体市場25年は予想以上に伸びるが26年はメモリが失速? ―― WSTS春季予測考察

- 微細化前倒しや3層積層の強化……「市場で勝ち切る」ソニーの半導体戦略

- イメージセンサー金額シェア60%目標「数年遅れる」、ソニー半導体

- センサーで微細プロセス、ロジックも12nm導入へ ソニーのイメージセンサー戦略

- 自動運転のキーデバイスとなる車載SoC

- キオクシアが攻める「NANDとDRAMのあいだ」 NVIDIAと協業も

- 次はデータセンター 「スマホ以外」にも手を広げるQualcomm

- ソニーが「最速」のSPAD距離センサー開発、自動運転L3以上へ

- AMDがAI新興Untether AIのエンジニアチーム「だけ」買収

一度消えたPCMが「3D XPointメモリ」で劇的にカムバック

一度消えたPCMが「3D XPointメモリ」で劇的にカムバック 次世代メモリ技術の最有力候補はPCMとMRAM、ReRAM

次世代メモリ技術の最有力候補はPCMとMRAM、ReRAM HDD大手Seagateの2019年1~3月業績は2桁減収、利益は半分に

HDD大手Seagateの2019年1~3月業績は2桁減収、利益は半分に Intelの創業10年目(1977年):5V単一電源で動くUV-EPROMを発表

Intelの創業10年目(1977年):5V単一電源で動くUV-EPROMを発表 InfineonのCypress買収は“弱点の克服”を狙う一手

InfineonのCypress買収は“弱点の克服”を狙う一手