EUVリソグラフィを補完する自己組織化リソグラフィ:福田昭のデバイス通信(293) Intelが語るオンチップの多層配線技術(14)(1/2 ページ)

今回は、自己組織化リソグラフィがEUV(極端紫外線)リソグラフィの弱点を補完する技術であることを説明する。

自己組織化とEUVの組み合わせが最適なソリューションと主張

半導体のデバイス技術と回路技術に関する国際学会「VLSIシンポジウム」では、「ショートコース(Short Course)」と呼ぶ技術講座を開催してきた。2020年6月に開催されたVLSIシンポジウムのショートコースは、3つの共通テーマによる1日がかりの技術講座が設けられていた。その中で「SC1:Future of Scaling for Logic and Memory(ロジックとメモリのスケーリングの将来)」を共通テーマとする講演、「On-Die Interconnect Challenges and Opportunities for Future Technology Nodes(将来の技術ノードに向けたオンダイ相互接続の課題と機会)」が非常に興味深かった。そこで講演の概要を本コラムの第280回からシリーズでお届けしている。講演者はIntelのMauro J. Kobrinsky氏である。

なお講演の内容だけでは説明が不十分なところがあるので、本シリーズでは読者の理解を助けるために、講演の内容を適宜、補足している。あらかじめご了承されたい。

本シリーズの前々回(第12回)から、ArF液浸技術やEUV技術などの露光技術の微細化限界を超える、あるいはこれらの露光技術を延命させる次世代のリソグラフィ技術「自己組織化リソグラフィ(DSAリソグラフィ)」の講演部分を紹介している。

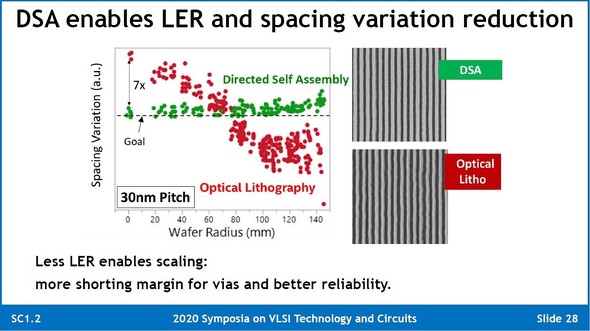

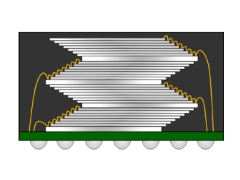

前回では、自己組織化リソグラフィ(DSAリソグラフィ)による微細なパターンの形成プロセスと、微細パターンの試作例をご報告した。今回は、DSAリソグラフィがEUV(極端紫外線)リソグラフィの弱点を補完する技術であることを説明する。講演では、DSAリソグラフィがEUVリソグラフィを補完することで、EUVリソグラフィの性能を最大化できると主張していた。

その理由は、配線パターンのばらつきを減らせることにある。DSAリソグラフィは同じ分子長の共重合高分子材料を使うので、自己集合によって立体的な構造を形成したときに、原理的には幅のばらつきがない。従って最先端の光リソグラフィやEUVリソグラフィなどでは大きな障害となる、配線幅のばらつき(LWR:Line Width Roughness)および配線端部の凹凸(LER:Line Edge Roughness)の問題がDSAリソグラフィでは理論的には生じない。

Copyright © ITmedia, Inc. All Rights Reserved.

Special Contents

- PR -- 逕」讌ュ逕ィ讖溷勣�剰ィュ蛯吶�螳牙ョ夂ィシ蜒阪→髟キ蟇ソ蜻ス蛹悶r螳溽樟縲�崕貅舌�繝ォ繧ケ繝「繝九ち繝ェ繝ウ繧ー縺ョ蠑キ蛹也ュ�

- GaN縲ヾiC繝代Ρ繝シ蜊雁ー惹ス薙�謚陦馴擠譁ー縲PCIM 2025繝ャ繝昴�繝遺補暮崕蟄千沿2025蟷エ8譛亥捷

- 繧、繝。繝シ繧ク繧サ繝ウ繧オ繝シ縺�縺代§繧�↑縺�蜿守寢貅舌r謗「繧九た繝九�縺ョ蜊雁ー惹ス捺姶逡・

- 菴山DS��on�臥音諤ァ縺ィ蠎�>螳牙�蜍穂ス憺�伜沺��SOA�峨r荳。遶九☆繧九ヱ繝ッ繝シMOSFET縺ョ螳溷鴨縺ィ縺ッ��

- 48V/54V蟇セ蠢懊ワ繧、繝悶Μ繝�ラ髯榊悸繧ウ繝ウ繝舌�繧ソ繝シ縲�崕貅占ィュ險医r縺ゥ繧後□縺醍ー。邏�蛹悶〒縺阪k��

Special Contents 1

- PR -Special Contents 2

- PR -記事ランキング

- 車載半導体ランキング、首位はInfineonでルネサスは5位

- HBMの代替どころか、勇み足で終わりかねない「HBF」

- Intel低迷でSamsungが笑う? パッケージングのエース級人材が移籍

- 「あえてレガシー半導体」のSkyWater Infineon工場買収で生産能力4倍に

- TSMCが6インチウエハー製造を段階的に停止へ

- 米国半導体の強化は100%関税よりIntel支援 ── 分社発表から1年、結論を急げ

- 「コイン1枚に5トンのゾウ4頭分」の応力を制御、300mm GaNウエハーの量産近づく

- 「ファウンドリー事業完全放棄の可能性」、Intel CEOが言及

- チップ分解で20年をたどる 「万華鏡」のように変化し続ける半導体業界

- 「AppleがSamsungから半導体調達」報道、ソニーの反応は